Single Chip Solution for Capacitance Measurement Volume 1: General Data and Front-End Description

July 16<sup>th</sup> , 2013, Version 1.3

Document-No: DB\_PCapØ2A\_Vol1\_en.pdf

### Published by acam-messelectronic qmbh

©acam-messelectronic ambh 2013

# Limitation of Liability/ Warranty/ Copyright

The information and data contained in this document are believed to be accurate and reliable, acam assumes no liability for errors and gives no warranty representation or quarantee regarding the suitability of its products for any particular purpose due to these specifications. Any information and data which may be provided in the document can and do vary in different applications, and actual performance may vary over time. All operating parameters must be validated for each customer application by customers' technical experts.

The information contained therein may be protected by copyright, patent, trademark and/or other intellectual property rights of acam, acam does not assume responsibility for patent infringements or other rights of third parties which may result from its use.

acam reserves the right to review this document and to make changes to the document's content at any time without obligation to notify any person or entity of such revision or changes. "Preliminary" product information describes a product which is not in full production so that full information about the product is not available yet.

Do not use our products in life-supporting systems, aviation and aerospace applications! Unless explicitly agreed to otherwise in writing between the parties, acam' products are not designed, intended or authorized for use as components in systems intended for surgical implants into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the product could create a situation where personal injury or death could occur.

No part of this publication may be reproduced, photocopied, stored on a retrieval system or transmitted without the express written consent of acam.

All rights not expressly granted remain reserved by acam. **JEAM**, **PICO**STRAIN, **PICO**CAP and FICOTURN are registered trademarks of acam. All other brand and product names in this document are trademarks or service marks of their respective owners.

### Support / Contact

For a complete listing of Direct Sales, Distributor and Sales Representative contacts, visit the acam web site at:

http://www.acam.de/sales/distributors/

For technical support you can contact the acam support team in the headquarters in Germany or the Distributor in your country. The contact details of acam in Germany are:

support@acam.de or by phone

+49-7244-74190.

# Content

| 1 Ov  | erview                                | 1-1  |

|-------|---------------------------------------|------|

| 1.1   | Features                              | 1-1  |

| 1.2   | Applications                          | 1-2  |

| 1.3   | Blockdiagram                          | 1-2  |

| 2 Ch  | aracteristics & Specifications        | 2-1  |

| 2.1   | Electrical Characteristics            | 2-1  |

| 2.2   | CDC Precision                         | 2-2  |

| 2.3   | RDC Precision                         | 2-3  |

| 2.4   | Internal RC-Oscillator                | 2-3  |

| 2.5   | Power Consumption                     | 2-4  |

| 2.6   | Package Information                   | 2-5  |

| 2.7   | QFN Packages                          | 2-7  |

| 3 Co  | nverter Frontend                      | 3-1  |

| 3.1   | CDC, Capacitance-to-Digital Converter | 3-1  |

| 3.2   | CDC Compensation Options              | 3-7  |

| 3.3   | CDC Important Parameters              | 3-9  |

| 3.4   | RDC Resistance-to-Digital Converter   | 3-12 |

| 3.5   | RDC Important Parameters              | 3-15 |

| 4 Int | erfaces (Serial & PDM/PWM)            | 4-1  |

| 4.1   | Serial Interfaces                     | 4-1  |

| 4.2   | I <sup>2</sup> C Compatible Interface | 4-2  |

| 4.3   | SPI interface                         | 4-3  |

| 4.4   | Special Timings                       | 4-5  |

| 4.5   | OTP Timings                           | 4-7  |

| 4.6   | GPIO and PDM/PWM                      | 4-10 |

| 4.7   | Interfaces Parameters                 | 4-15 |

| 5 Co  | nfiguration & Read Registers          | 5-1  |

| 5.1   | Configuration registers               | 5-1  |

| 5.2   | Configuration Registers in Detail     | 5-4  |

| 5.3   | Oscillator Configuration              | 5-20 |

| 5.4   | Low Battery Detection (LBD)           | 5-21 |

| 5.5   | Read Registers                        | 5-22 |

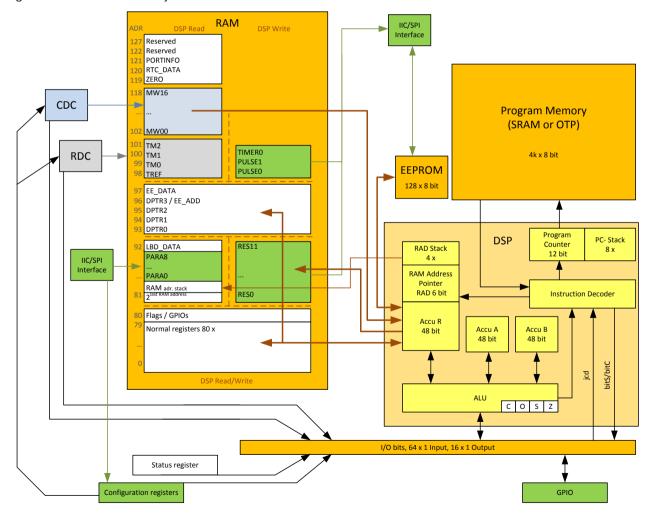

| 6 DS  | SP & Memory                           | 6-1  |

| 6.1   | Memory Map                            | 6-2  |

| 6.2   | Memory Management                     | 6-3  |

| 6.3   | Getting started                       | 6-5  |

# PCapØ2A

| 7 | Mis | cellaneous                                                  | 7-1 |

|---|-----|-------------------------------------------------------------|-----|

|   | 7.1 | Bug Report                                                  | 7-1 |

|   | 7.2 | I <sup>2</sup> C Bug with POR directly after rd/wr OTP/SRAM | 7-1 |

|   | 7.3 | Limitation of Parameter2                                    | 7-1 |

|   | 7 4 | History                                                     | 7-2 |

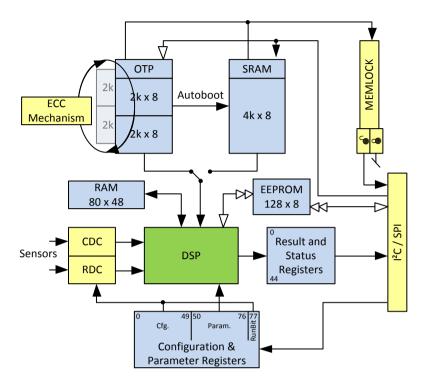

## 1 Overview

PCapØ2Y is a capacitance-to-digital converter (CDC) with integrated digital signal processor (DSP) for on-chip data post-processing. Its front end is based on acam's patented PICDCAP® principle. This conversion principle offers outstanding flexibility with respect to power consumption, resolution and speed. This datasheet describes PCapØ2A, in its basic converter functionality. The DSP description is reduced to the standard firmware that calculates pure capacitance ratios. A detailed DSP and memory description is given in datasheet volume 2. PCapØ2 can be used for single and differential sensors in grounded and floating application. Compensation of internal and external stray capacitance is implemented as well as for parallel resistance. Additionally, the temperature can be measured by means of internal thermistors or external sensors.

#### 1.1 Features

- Digital measuring principle in CMOS technology

- Up to 8 capacitances in grounded mode

- Up to 4 capacitances in floating mode (potential- free and with zero bias voltage)

- Integrated reference capacitance 1 pF to 31 pF

- Integrated discharge resistors up to 1 M0hm

- Compensation of internal (grounded) and external parasitic capacities (floating)

- Pre-charge option for slow charging

- Self-test capability for differential sensors

- High resolution: up to 15 aF at 2.5 Hz and 10 pF base capacitance or, 17 bit resolution at 5 Hz with 100 pF base capacitance and 10 pF excitation

- High measurement rate: up to 500 kHz

- Extremely low current consumption possible: Down to 2.5 μA at 2.5 Hz with 13.1 bit resolution

- High stability with temperature, low offset drift (down to 20 aF per Kelvin), low gain drift when all compensation options are activated.

- Dedicated ports for precision temperature measurement (with Pt1000 sensors, the resolution is 0.005 K)

- Serial interface (SPI or IIC compatible)

- Two 10/12/14/16 bit PDM/PWM outputs for analog interfaces

- Self-boot capability

- Single power supply (2.1 to 3.6 V), integrated 1.8 V regulator for improved PSRR.

- Integrated voltage measurement

- No need for a clock

- RISC processor core using Harvard architecture:

- 128 x 48/24 bit RAM Data (80x48 free)

- 4k x 8 bit SRAM program memory for high-speed operation (40 to 85 MHz)

- 4k (+4k for ECC)x 8 bit OTP (one-time programmable) program memory for normal speed operation (up to 40 MHz)

- 128 byte EEPROM for calibration data and user data (serial number etc.)

### 1.2 Applications

- Humidity sensors

- Position sensors

- Pressure sensors

- Force sensors

- Acceleration sensors

- Inclination sensors

- Tilt sensors

- Angle sensors

- Wireless applications

- Level sensors

- Microphones

- MEMS sensors

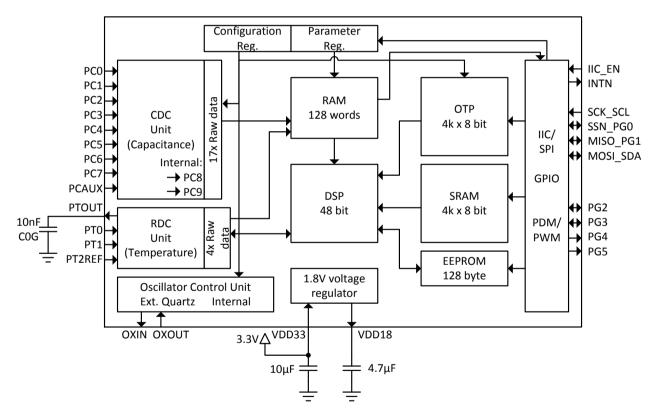

# 1.3 Blockdiagram

Figure 1-1 Blockdiagram

# 2 Characteristics & Specifications

### 2.1 Electrical Characteristics

## 2.1.1 Absolute Maximum Ratings

Supply voltage  $V_{DD}$ -to-GND - 0.3 to 4.0 V

Storage temperature Tstg - 55 to 150 °C

ESD rating (HBM), each pin > 2 kV

Junction temperature (Tj) max. 125 °C

OTP Data Retention Period 10 years at 95 °C temperature

EEPROM Data Retention Period 10 years at 95 °C temperature

# 2.1.2 Recommended Operating Conditions

Table 2-1 Operating conditions

| Quantity                       | Sym-<br>bol          | Remarks                                                                              | Min.  | Тур.                                           | Max.                          | Unit |

|--------------------------------|----------------------|--------------------------------------------------------------------------------------|-------|------------------------------------------------|-------------------------------|------|

| Supply voltage                 | V <sub>DD</sub>      |                                                                                      | 2.1   |                                                | 3.6                           | V    |

| Digital<br>port voltage        | Vio_digital          | Relative to ground                                                                   | - 0.6 | 3.3                                            | V <sub>DD</sub> +0.6<br>≤ 3.6 | V    |

| Digital ports switching level  |                      | HIGH → LOW<br>LOW → HIGH                                                             |       | 0.3 * V <sub>DD</sub><br>0.7 * V <sub>DD</sub> |                               |      |

| Analog port voltage            | Vio_analog           |                                                                                      | - 0.6 |                                                | V <sub>DD</sub> +0.6<br>≤ 3.6 | V    |

| OTP<br>Programming<br>voltage  | Vотр                 | Between "VPP_OTP" port and ground. Do not expose other ports to programming voltage. |       | 6.5                                            | 7.0                           | V    |

| SPI bus frequency              | f <sub>SPI-bus</sub> | Clock frequency for the 4-<br>wire SPI bus operation                                 | 0     |                                                | 20                            | MHz  |

| I <sup>2</sup> C bus frequency |                      | Speed (data rate) of the<br>2-wire I <sup>2</sup> C bus operation                    | 0     |                                                | 100                           | kHz  |

| OTP Bit hold time              |                      | Bit hold time for OTP write                                                          | 30    |                                                | 500                           | μs   |

| GPIO input rise<br>time        |                      | Rise time of the input signal put to general-purpose I/O                             |       |                                                | 500                           | ns   |

| GPIO output rise<br>time       |                      | Rise time of the output signal from a general-purpose I/O                            |       | 6                                              | t.b.d.                        | ns   |

| CDC discharge |    | MR1                     | 0    | 40    | μs |

|---------------|----|-------------------------|------|-------|----|

| time          |    |                         |      |       |    |

| RDC discharge |    |                         | 0    | 100   | μs |

| time          |    |                         |      |       |    |

| Junction      | Tj | Junction temperature    | - 40 | + 125 | °C |

| Temperature   |    | must not exceed +125 °C |      |       |    |

| Ambient       | Ta | At VDD = 2.4V -/+ 0.3V  | - 40 | + 125 | °C |

| Temperature   |    |                         |      |       |    |

#### 2.2 CDC Precision

## 2.2.1 RMS Noise and Resolution vs. Output Data Rate

Table 2-2 Typical capacitive noise & resolution vs. output data rate, 10 pF base + 1 pF span, fast settle, MR1, V = 3.0 V

| Output<br>Data | FLOATING Fully compensated |                                   |                                           | GROUNDED Internally compensated |                                           |                                           |

|----------------|----------------------------|-----------------------------------|-------------------------------------------|---------------------------------|-------------------------------------------|-------------------------------------------|

| Rate<br>[Hz]   | RMS<br>Noise<br>[aF]       | Eff. Resolution 10 pF base [Bits] | Eff.<br>Resolution<br>1 pF span<br>[Bits] | RMS<br>Noise<br>[aF]            | Eff. Resolu-<br>tion 10 pF<br>base [Bits] | Eff.<br>Resolution<br>1 pF span<br>[Bits] |

| 2.5            | 15                         | 19.3                              | 16.0                                      |                                 |                                           |                                           |

| 5              | 23                         | 18.7                              | 15.4                                      | 15                              | 19.3                                      | 16.0                                      |

| 10             | 35                         | 18.1                              | 14.8                                      | 23                              | 18.7                                      | 15.4                                      |

| 25             | 48                         | 17.7                              | 14.4                                      | 50                              | 17.6                                      | 14.3                                      |

| 100            | 134                        | 16.2                              | 12.9                                      | 81                              | 16.9                                      | 13.6                                      |

| 250            | 172                        | 15.8                              | 12.5                                      | 116                             | 16.4                                      | 13.1                                      |

| 1,000          | 330                        | 14.9                              | 11.6                                      | 147                             | 16.0                                      | 12.7                                      |

| 2,000          | 438                        | 14.5                              | 11.2                                      | 230                             | 15.4                                      | 12.1                                      |

| 4,000          | 603                        | 14.0                              | 10.7                                      | 327                             | 14.9                                      | 11.6                                      |

| 10,000         | 838                        | 13.5                              | 10.2                                      | 566                             | 14.1                                      | 10.8                                      |

| 25,000         |                            |                                   |                                           | 817                             | 13.6                                      | 10.3                                      |

The table gives the root mean-square (RMS) noise in aF as a function of output data rate in Hz, measured at 3.0 V supply voltage using the maximum possible sample size for inchip averaging at the minimum possible cycle time. Bit values are calculated as a binary logarithm of noise over the span (BITs =  $\ln(\text{span/noise})/\ln(2)$ ). The measurements have been done with the PCapØ2 evaluation board, with fixed COG ceramic capacitors.

Both, sensor and reference are connected "floating" or "grounded", as indicated. When floating, compensation mechanisms for both internal and external stray capacitances are activated, when grounded, internal ones only.

### 2.2.2 RMS Noise vs. Supply Voltage

Figure x RMS Noise vs. Supply Voltage - to follow

Note: Buffer capacitors of sufficient capacitance are mandatory for good measurement quality. We recommend to use minimum 10  $\mu F$  COG for VDD33 and 4.7  $\mu F$  for VDD18\_OUT.

## 2.2.3 Voltage-Dependent Offset and Gain Error (PSRR)

Figure x Gain Error in % vs. Supply Voltage (Power Supply Rejection Ratio) - to follow

### 2.2.4 Temperature-Dependent Offset and Gain Error

Figure x Offset Drift vs. Temperature – to follow

Figure x Gain Drift vs. Temperature - to follow

### 2.3 RDC Precision

Table 2-3 Thermoresistive coefficients Tk at 20 °C

| Material                        | Tk         |

|---------------------------------|------------|

| Internal poly-silicon reference | -1.1 ppm/K |

| Internal aluminum thermistor    | 2830 ppm/K |

| External PT1000 sensor          | 3830 ppm/K |

Table 2-4 Noise with internal Al/PolySi at 20 °C

| Measurement          | R2/Rref typ. | RMS noise | Typical RMS noise (*) |

|----------------------|--------------|-----------|-----------------------|

| Conditions           |              | R2/Rref   | Temperature           |

| No averaging, 2 fake | 0.825        | 50 ppm    | 25 mK                 |

| measurements         |              |           |                       |

| 16-fold averaging, 8 | 0.823        | 10 ppm    | 5 mK                  |

| fake measurements    |              |           |                       |

<sup>(\*)</sup> after linearization in post-processing software

#### 2.4 Internal RC-Oscillator

The integrated RC-Oscillator can be set in the range between 10 kHz and 200 kHz, in which 50 kHz is the standard setting (see Register 3 description) and section 5.3.

The nominal frequency e.g. 50 kHz has a standard deviation of +/-20 % over parts.

More than that, the internal oscillator is dependent on voltage and temperature.

## 2.5 Power Consumption

Table 2-5 Total current I  $[\mu A]$  as a function of conversion rate (CONV\_TIME) and resolution (C\_AVRG) in triggered mode

| OLF   | CONV_ | Measure   | Ι [μΑ]                         |      |      |      |      |      |

|-------|-------|-----------|--------------------------------|------|------|------|------|------|

| Freq. | TIME  | rate [Hz] | C_AVRG (RMS resolution [Bits]) |      |      |      |      |      |

| [kHz] |       |           | 1                              | 4    | 16   | 64   | 256  | 1024 |

|       |       |           | 13.1                           | 14.2 | 15.1 | 16.0 | 16.6 | 17.5 |

| 50    | 10000 | 2.5       | 2.5                            | 2.7  | 2.9  | 3.9  | 8.5  | 33   |

| 50    | 2500  | 10        | 3.1                            | 3.3  | 3.7  | 8.3  | 20   | 32   |

| 50    | 1250  | 20        | 3.9                            | 5    | 7    | 15   | 26   |      |

| 50    | 625   | 40        | 5.6                            | 7    | 11   | 29   |      |      |

| 50    | 250   | 100       | 11                             | 13   | 24   |      |      |      |

| 50    | 125   | 200       | 19                             | 27   |      |      |      |      |

| 50    | 50    | 500       | 43                             | 57   |      |      |      |      |

| 50    | 25    | 1000      | 84                             |      |      |      |      |      |

| 50    | 12    | 2080      | 172                            | _    |      |      |      |      |

| 200   | 24    | 4160      | 348                            |      |      |      |      |      |

| 200   | 12    | 9320      | 689                            |      |      |      |      |      |

Temperature measurement in addition to capacitive measurement will add between 2 and 10  $\mu$ A approximately, depending on speed. Total consumption values below 30  $\mu$ A may be obtained only when driving the on-chip 1.8 volts core supply generator in an energy-saving mode; ultimate microampere savings also demand to slow down the DSP.

### 2.6 Package Information

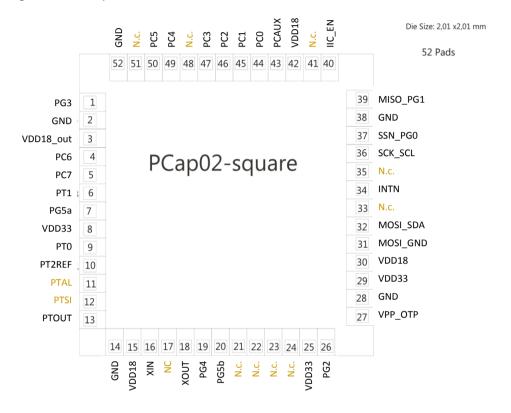

## 2.6.1 Dice - Pad Layout

Die dimensions: 2.01 mm x 2.01 mm with pad pitch 120  $\mu$ m, pad opening is 85  $\mu$ m x 85  $\mu$ m, Thickness 290  $\mu$ m.

Figure 2-1 Pad positions on die

Table 2-6 Pad description

| Pad | Name      | X-Pos(µm) | Y-Pos(µm) | Туре |

|-----|-----------|-----------|-----------|------|

| 1   | PG3       | 44.5      | 1680.0    |      |

| 2   | GND       | 44.5      | 1560.0    |      |

| 3   | VDD18_out | 44.5      | 1440.0    |      |

| 4   | PC6       | 44.5      | 1320.0    |      |

| 5   | PC7       | 44.5      | 1200.0    |      |

| 6   | PT1       | 44.5      | 1080.0    |      |

| 7   | PG5a      | 44.5      | 960.0     |      |

| 8   | VDD33     | 44.5      | 840.0     |      |

| 9   | PTO       | 44.5      | 720.0     |      |

| 10  | PT2REF    | 44.5      | 600.0     |      |

| 11  | PTAL      | no pad    | no pad    |      |

| 12  | PTSI      | no pad    | no pad    |      |

| 13  | PTOUT     | 44.5      | 240.0     |      |

| 14  | GND       | 270.0     | 44.5      |      |

| 15  | VDD18     | 390.0     | 44.5      |      |

| 16  | XIN       | 510.0     | 44.5      |      |

| 17  | n.c.      | no pad    | no pad    |      |

| Pad | Name     | X-Pos(µm) | Y-Pos(µm) | Туре     |

|-----|----------|-----------|-----------|----------|

| 18  | XOUT     | 750.0     | 44.5      | <b>,</b> |

| 19  | PG4      | 870.0     | 44.5      |          |

| 20  | PG5      | 990.0     | 44.5      |          |

| 21  | TESTO    | 1170.0    | 44.5      |          |

| 22  | TEST1    | 1290.0    | 44.5      |          |

| 23  | TEST2    | 1410.0    | 44.5      |          |

| 24  | TEST3    | 1530.0    | 44.5      |          |

| 25  | VDD33    | 1650.0    | 44.5      |          |

| 26  | PG2      | 1770.0    | 44.5      |          |

| 27  | VPP_OTP  | 1965.5    | 240.0     |          |

| 28  | GND      | 1965.5    | 360.0     |          |

| 29  | VDD33    | 1965.5    | 480.0     |          |

| 30  | VDD18    | 1965.5    | 600.0     |          |

| 31  | GND      | 1965.5    | 720.0     |          |

| 32  | MOSI_SDA | 1965.5    | 840.0     |          |

| 33  | TEST4    | 1965.5    | 960.0     |          |

| 34  | INTN     | 1965.5    | 1080.0    |          |

| 35  | TEST5    | 1965.5    | 1200.0    |          |

| 36  | SCK_SCL  | 1965.5    | 1320.0    |          |

| 37  | SSN_PGO  | 1965.5    | 1440.0    |          |

| 38  | GND      | 1965.5    | 1560.0    |          |

| 39  | MISO_PG1 | 1965.5    | 1680.0    |          |

| 40  | IIC_EN   | 1770.0    | 1965.5    |          |

| 41  | TEST6    | 1650.0    | 1965.5    |          |

| 42  | VDD18    | 1530.0    | 1965.5    |          |

| 43  | PCAUX    | 1350.0    | 1965.5    |          |

| 44  | PCO      | 1230.0    | 1965.5    |          |

| 45  | PC1      | 1110.0    | 1965.5    |          |

| 46  | PC2      | 990.0     | 1965.5    |          |

| 47  | PC3      | 870.0     | 1965.5    |          |

| 48  | TTES7    | 750.0     | 1965.5    |          |

| 49  | PC4      | 630.0     | 1965.5    |          |

| 50  | PC5      | 510.0     | 1965.5    |          |

| 51  | TEST8    | 390.0     | 1965.5    |          |

| 52  | GND      | 270.0     | 1965.5    |          |

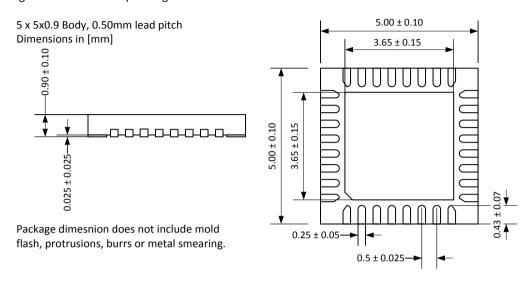

### 2.7 QFN Packages

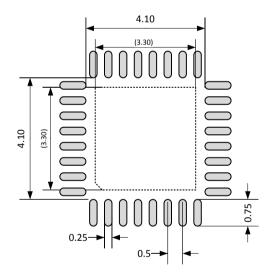

Figure 2-2 QFN32 package dimensions

Dimensioning and tolerances acc. to ASME Y14.5M-1994

### Landing pattern (dimensions in [mm]):

Caution: Center pad is internally connected to GND. No wires other than GND are allowed underneath.

It is recommended to not use the center pad. Too much solder paste could reduce solder quality.

Suitable socket:

e.g. Plastronics 32QN50S15050D

**Thermal resistance:** Roughly 28 K/W (value just for reference).

**Environmental:** The package is RoHS compliant and does not contain any critical materials according to REACH regulation (EG) No. 1907/2006.

**Moisture Sensitive Level (MSL):** Based on JEDEC 020 Moisture Sensitivity Level definition the PCapØ2 is classified as MSL 3.

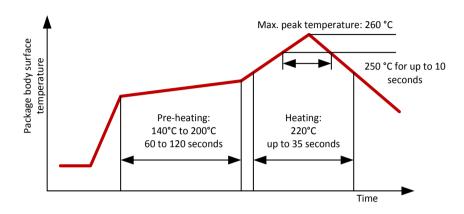

### **Soldering Temperature Profile**

The temperature profile for infrared reflow furnace (in which the temperature is the resin's surface temperature) should be maintained within the range described below.

Figure 2-8: Soldering profile

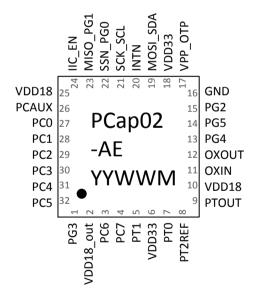

### 2.7.1 Pin-Out QFN32

Figure 2-3 QFN32 Pin-out

The center pad on the bottom of the QFN package is internally connected to GND.

Connecting to ground on the PCB is not mandatory, and for reliable soldering it should not be connected.

# 2.7.3 Pin/Pad Assignment

Table 2-7 Pin Description

| Pin       | Description                            | Comment | Pin# |

|-----------|----------------------------------------|---------|------|

| PG3       | General purpose I/O port               |         | 1    |

| VDD18_out |                                        |         | 2    |

| PC6       | Capacitance port                       |         | 3    |

| PC7       | Capacitance port                       |         | 4    |

| PT1       | Resistance port (temperature sensor)   |         | 5    |

| VDD33     |                                        |         | 6    |

| PTO       | Resistance port (temperature sensor)   |         | 7    |

| PT2REF    | Resistance port (temp. sensor, refer.) |         | 8    |

| PTOUT     | Port to connect 10 nF discharge        |         | 9    |

|           | capacitor for resistance measurement   |         |      |

| VDD18     |                                        |         | 10   |

| OXIN      | Oscillator port                        |         | 11   |

| OXOUT     | Oscillator port                        |         | 12   |

| PG4       | General purpose I/O port               |         | 13   |

| PG5       | General purpose I/O port               |         | 14   |

| PG2       | General purpose I/O port               |         | 15   |

| GND       |                                        |         | 16   |

| VPP_OTP   |                                        |         | 17   |

| VDD33     |                                        |         | 18   |

| MOSI_SDA  | Master out/Slave in when SPI is used.  |         | 19   |

|           | Otherwise, Serial data out for IIC     |         |      |

| INTN      | Interrupt, Low active                  |         | 20   |

| SCK_SCL   | Serial clock for SPI/IIC               |         | 21   |

| SSN_PGO   | Serial Select Line (Serial reset).     |         | 22   |

|           | Otherwise, general purpose I/O port    |         |      |

| MISO_PG1  | Master in/Slave out when SPI is used.  |         | 23   |

|           | Otherwise, general purpose I/O port    |         |      |

| IIC_EN    | O = SPI enable, 1 = IIC enable         |         | 24   |

| VDD18     |                                        |         | 25   |

| PCAUX     | Capacitance port                       |         | 26   |

| PCO       | Capacitance measurement port           |         | 27   |

| PC1       | Capacitance measurement port           |         | 28   |

| PC2       | Capacitance measurement port           |         | 29   |

| PC3       | Capacitance measurement port           |         | 30   |

| PC4       | Capacitance measurement port           |         | 31   |

| PC5       | Capacitance measurement port           |         | 32   |

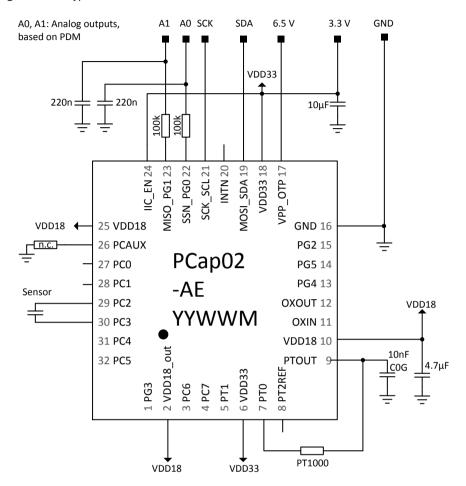

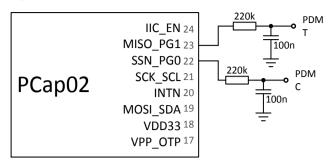

### 2.7.4 Typical Schematics

Figure 2-4 Typical schematics, I<sup>2</sup>C interface, internal references.

# 3 Converter Frontend

The device uses "discharge time measurement" as a principle for measuring either capacitance (CDC unit) or resistance (RDC unit). It addresses all ports (PC...,PT...) in time multiplex, CDC and RDC measurements possibly running in parallel. The time measurement is done by means of a high-resolution TDC (time-to-digital converter).

# 3.1 CDC, Capacitance-to-Digital Converter

# 3.1.1 Measuring Principle

In PCapØ2 capacitance measurement is done by measuring discharge times of RC-networks. The measurements are ratiometric. This means the capacitors are compared to a fixed reference or, like in differential sensors, to capacitors with change in opposite direction. Thanks to the short time intervals and special compensation methods, the ratio of discharge times is directly proportional to the ratio of capacitors. The discharge time is defined by the capacitor and the selected discharge resistor.

$$\frac{\tau_N}{\tau_{ref}} = \frac{C_N}{C_{ref}} \qquad \qquad \tau = k * R * C$$

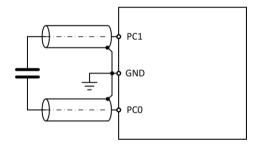

### 3.1.2 Connecting Sensors

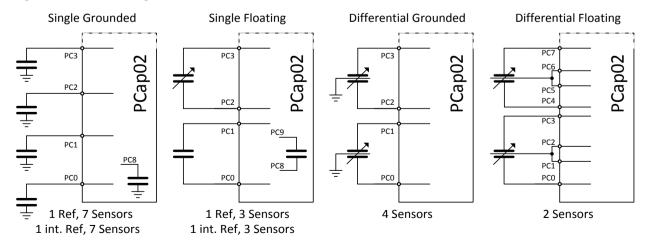

PCapØ2 can handle single and differential sensors in grounded or floating connection.

Additionally to the known PCapØ1 options, PCapØ2 has integrated reference capacitors.

Those can be used with single sensors. They are programmable in a range from 1 to 31pF in steps of 1 pF.

Figure 3-1 Connecting sensors

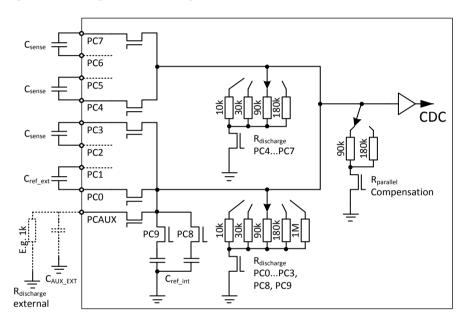

### 3.1.3 Discharge Resistors

The PCapØ2A has two sets of discharge resistors already integrated. One resistor set (10k, 30k, 90k, 180k, 1000k) is for measurements on port PCO to PC3 and the internal reference ports PC8 and PC9. The other resistor set (10k, 30k, 90k, 180k) is for ports PC4 to PC7. This way, it is possible to measure different sensors with strongly deviated capacitance like pressure and humidity with one and the same chip. The resistors are selected by parameters RCHG\_xxx.

Figure 3-2 Integrated discharge resistors

Some applications like humidity sensors may demand a very slow discharge. For this reason the 1 MOhm discharge resistor is integrated. It is selected by RDCHG\_1MEG\_EN.

For big capacitances there is the possibility to use an external discharge resistor.

### 3.1.4 Cycle

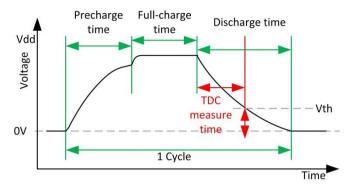

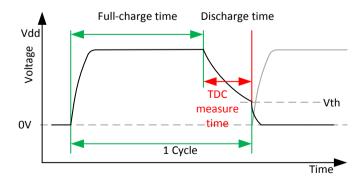

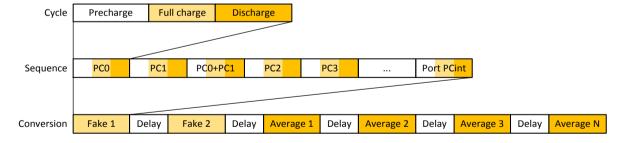

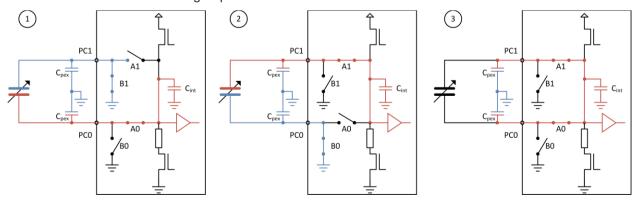

In PCapØ2 the measuring principle was greatly improved by introducing a pre-charge phase. In the very first step, the capacitor is charged up via a series resistor to a level close to Vdd. The resistor reduces the charge current and reduces the mechanical stress on the sensing capacitor. This can be necessary in some MEMS applications. In a second step, the capacitor is charged up finally to Vdd without a series resistor. Then, in the third step, the capacitor is discharged via the discharge resistor down to OV. The CDC measures the time interval until a trigger level is reached. All this is called a single "cycle".

Figure 3-3 Single Cycle Timing

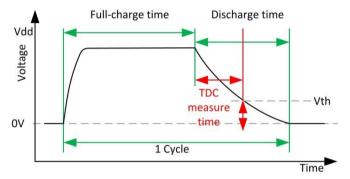

In applications that don't need the slow charge up but high conversion rate, it is possible to disable the pre-charge option and to start charge up directly without any series resistor.

Figure 3-4 Single Cycle, fast charge

In both cases the capacitors are discharged for the full discharge time period and then connected to GND.

Finally, there is an option to operate the chip in PCapØ1 compatible mode. This means, as soon as the trigger level of the discharge time measurement is reached, the current port is immediately connected to GND and the next port will be charged up to Vdd.

Figure 3-5 Single Cycle, PCapØ1compatible

### 3.1.5 Sequence

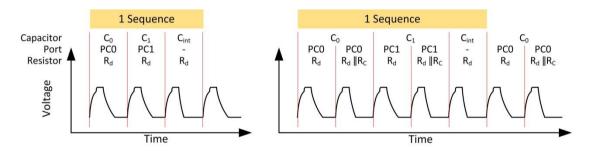

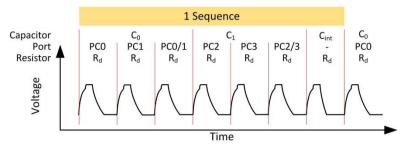

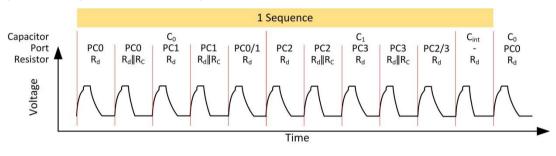

A "sequence" is made of a set of cycles, namely those for the various active ports as well as combinations of them as given by the compensation measurements. The number and kind of single cycles depends on the way of connecting the sensors, the number of capacitors and the selected compensation options.

For **grounded** sensors, the sequence starts always with PCO (reference) and then one or more of the other 7 ports. Normally, internal compensation is activated. So the sequence ends with the measurement C<sub>int</sub> of the internal stray capacitance/delays. For compensating internal parasitic capacitance and the comparator delay the CDC measures the discharge time with all ports being off (C<sub>int</sub>).

For compensating parallel resistances to the capacitors, the CDC measures the discharge time for each capacitor a second time.

The following figure shows the sequence for a grounded sensor with internal compensation and in case of parallel resistance compensation.

Figure 3-6 Sequence for 1 reference & 1 sensor in grounded connection, compensated for internal capacitance, and – one the right side – compensation for parallel resistances

For **floating** sensors, the sequence starts always with PCO/PC1 (reference), followed by one to three pairs of ports for the sensors. Normally, full compensation (internal and external) is activated.

For compensation of external parasitic capacitances the CDC makes a measurement for each capacitor with both ports being opened. So, for each capacitor 3 measurements are made, e.g. PCO, PC1 and PCO+PC1. In case of parallel-resistance compensation there are 5 measurements for each capacitor. The sequence ends with the internal compensation measurement C<sub>int</sub>. The following figures show the sequence for 1 floating sensor with full compensation.

Figure 3-7 Sequence for 1 reference & 1 sensor in floating connection, fully compensated for parasitic capacitances

Figure 3-8 Sequence for 1 reference & 1 sensor in grounded connection, fully compensated for parasitic capacitances and for parallel resistances

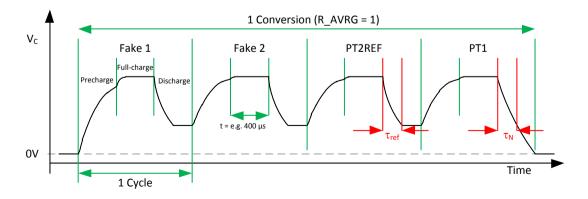

#### 3.1.6 Conversion

Finally, the combination of various sequences and delays in between the sequences define a single "conversion". At the end of a conversion the measurement results are ready for further processing and readout. The end of the conversion is indicated by flag to the DSP and also the RDC unit.

Figure 3-9 Cycle - Sequence - Conversion

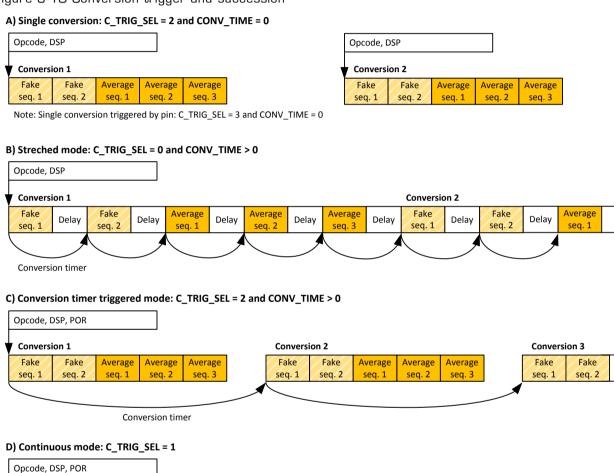

A conversion is triggered from outside the CDC unit:

- By the conversion timer

- Pin triggered

- By the DSP

- By serial interface (opcode).

Once triggered, a conversion is automatically completed, including all fake measurements and all real measurements defined by sample size for averaging. The end of the conversion is indicated to the master (DSP, timer, µP).

The way conversions follow each other is described by four principal operating modes:

Single conversion, Stretched mode, Conversion timer triggered mode and Continuous mode.

Figure 3-10 Conversion trigger and succession

Conversion 1

Fake

sea. 2

Average

Average

**Average**

Fake

seq. 1

Conversion 2

Fake

Average

**Average**

Average

Fake

sea. 1

**Conversion 3**

Fake

**Average**

Fake

seq. 1

### 3.2 CDC Compensation Options

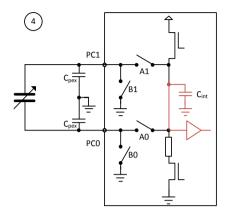

### 3.2.1 Internal Compensation

For the internal compensation measurement, both switches A1 and AO are open. Only the internal parasitic capacitance and the comparator propagation delay will thus be measured.

It is recommended to have internal compensation active in any application.

Figure 3-11 Internal compensation measurement

# 3.2.2 External Compensation

With floating capacitors we have the additional option to compensate external parasitic capacitances against ground. On the PCB, the wire capacitance typically refers to ground. For long wires, it is recommended to use shields which should be grounded at their PCB side.

Figure 3-12 How to connect shielded cables for compensation of the external parasitic capacitances.

Three measurements are necessary for each capacitor in case of floating sensors; this is shown in Figure 3-13.

Figure 3-13 Floating capacitors, external compensation measurements, the three measurements that are made for each floating capacitor.

#### 3.2.3 Parallel Resistance

In some applications the sensor might see a parallel resistance. This resistance is typically caused by dirt or condensation and is changing slowly. In PCapØ2A a compensation method is implemented to get rid of this.

# 3.2.4 Force Compensation & Self-test

For differential sensors, mainly MEMS, a force compensation method is available. In this mode the inactive electrode is connected to a dummy charge circuit and therefore always has a potential similar to that of the active electrode. The center electrode therefore is almost force free. Because the capacitances are different, the voltage is not the same upon reaching the trigger threshold, so there is a residual force.

This mode can be used for self-test, too. If force compensation is toggled, means measurements with and without compensation are made, then the force on the active electrode varies. The user should see an obvious difference between the measurement results with and without compensation. If not, then the sensor is most likely broken.

### 3.2.5 DC Balance

When driving floating sensors then the sensors' supply is typically DC free.

With parallel resistance compensation this symmetry would be broken. Therefore, PCapØ2 has the possibility to add dummy measurements so that even with parallel resistance compensation the sensors are operated DC free (set by C\_DC\_BALANCE).

In applications with grounded sensors the sensors can't be DC fee by principle.

#### 3.2.6 Gain Correction

Comparable to classical A/D converters, the PCapØ2 shows a gain error. But in case of PCapØ2 the gain error is mainly given by internal parasitic capacitances and the propagation delay of the internal comparator. With internal compensation being active this delay is subtracted from the original measurement. The temperature drift can be approximated linearly and corrected mathematically just by a gain factor. In the standard firmware parameter 8 is reserved for the gain correction factor. The correction factor depends on the discharge time and therefore the RC combination. The firmware has to take this factor into account, like the cdc.h library does. The factor is stored in parameter register 7 as Gain\_Corr. It has to be evaluated individually for every single application. E.g., with 22 pF and 30 kOhm the correction factor is 1.25.

### Empirical method to find the right gain correction factor:

Replace the sensor with a temperature stable capacitor of the same size (ceramic COG) as your reference capacitor. (Therefore: quotient = 1, gain = 0). Set the gain correction factor to 1.0. Put the system (PCapØ2 on PCB) into a temperature chamber and measure the offset drift over temperature. Add an additional temperature stable capacitor to simulate your gain. Measure the gain drift. Increase the gain correction factor and measure the gain drift again. With a gain correction factor >1.0 the gain drift will decrease. If the gain correction factor is set too big then you will see a negative gain drift due to over compensation. The right gain correction factor is found, if the drift is reduced to what you measured at the initial offset drift measurement. Write back the new Gain Corr value into parameter 7 register.

### 3.3 CDC Important Parameters

### 3.3.1 Cycle clock

The basic period t<sub>cycle</sub> that defines the cycle time can be derived from the low frequency oscillator or the high frequency oscillator. It is selected as in PCapØ1 by configuration parameters CY\_CLK\_SEL (register 11).

Table 3-1 Configure cycle clock, for details see register 11

| CY_CLK_SEL | Cycle time base                       |                                     |

|------------|---------------------------------------|-------------------------------------|

| 'b00       | t <sub>cycle</sub> = t <sub>OLF</sub> | tolf = period low-frequency oscil.  |

| 'b1O       | $t_{cycle} = 4*_{tOHF}$               | toнf = period high-frequency oscil. |

| 'b11       | t <sub>cycle</sub> = t <sub>OHF</sub> | toнғ = period high-frequency oscil. |

#### 3.3.2 Cycle time

The pre-charge, full-charge and discharge times of a single cycle are defined in multiples of toycle. Those are selected by:

Table 3-2 Configure cycle time, for detailsd see register 23-26

| Reg.   | Configuration   | Description                                                             |

|--------|-----------------|-------------------------------------------------------------------------|

|        | Parameter       |                                                                         |

| 25, 26 | PRECHARGE_TIME  | Time to charge via resistor for current limitation.                     |

|        |                 | O = no pre-charge phase                                                 |

|        |                 | 1 to 1023: tprecharg = PRECHARGE_TIME*tcycle                            |

| 27, 28 | FULLCHARGE_TIME | Time for final charge without current limitation.                       |

|        |                 | O = no full-charge phase                                                |

|        |                 | 1 to 1023: $t_{fullcharge}$ = (FULLCHARGE_TIME + 2) $\cdot$ $t_{cycle}$ |

| 23, 24 | DISCHARGE_TIME  | Time to discharge the capacitor.                                        |

|  | O = not allowed                                                       |

|--|-----------------------------------------------------------------------|

|  | 1 to 1023: $t_{discharge}$ = (DISCHARGE_TIME + 1) $\cdot$ $t_{cycle}$ |

In case that PRECHARGE\_TIME = FULLCHARGE\_TIME = 0 the timing is similar to PCap $\emptyset$ 1. Note: while in PCap $\emptyset$ 1 the times are set in 2's complement, in PCap $\emptyset$ 2 the times are set linearly and therefore can be set in finer steps.

### 3.3.3 Sequence

The length of a sequence depends on the kind and number of sensors, the selected compensation methods and the averaging sample size. The following parameters affect the sequence:

Table 3-3 Configure sequence, for details see registers 10 - 12

| Reg. | Configuration  | Description                                                                                                                                                             |  |  |  |  |  |  |  |

|------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|      | Parameter      |                                                                                                                                                                         |  |  |  |  |  |  |  |

| 12   | C_PORT_EN      | Bitwise enable of the capacitance ports PCO to PC7  O = Port disabled  1 = Port active                                                                                  |  |  |  |  |  |  |  |

| 10   | C_REF_INT      | Switches between external and internal reference capacitors. Can not be used with differential sensors.  O = external, PCO or PCO & PC1  1 = internal, PC8 or PC8 & PC9 |  |  |  |  |  |  |  |

| 10   | C_DIFFERENTIAL | Switches between single and differential sensors  O = single  1= differential                                                                                           |  |  |  |  |  |  |  |

| 10   | C_FLOATING     | Switches between grounded and floating sensors O = grounded 1 = floating                                                                                                |  |  |  |  |  |  |  |

| 10   | C_COMP_INT     | Turns on compensation of internal capacitances/delays O = off 1 = on, recommended                                                                                       |  |  |  |  |  |  |  |

| 10   | C_COMP_EXT     | Turns on compensation of external parasitic capacitances. Available only with floating sensors.  O = off 1 = on, recommended                                            |  |  |  |  |  |  |  |

| 10   | C_COMP_R       | Turns on compensation of parallel resistances  O = off  1 = on                                                                                                          |  |  |  |  |  |  |  |

| 11   | C_DC_BALANCE   | Turns on an additional measurement for DC balance. Introduces one additional measurement per capacitor. Effective in modes other than single grounded. O = off 1 = on   |  |  |  |  |  |  |  |

| 10   | C_COMP_FORCE   | Turns on force compensation for differential sensors  O = off, inactive electrode HiZ  1 = on, inactive electrode connected to dummy charge                             |  |  |  |  |  |  |  |

#### 3.3.4 Conversion

The duration of a full conversion has a lower limit given by the number of fake measurements, the averaging and eventually an inter-sequence delay:

Table 3-4 Configure conversion, for details see registers 13ff, 26

| Reg.   | Configuration<br>Parameter | Description                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|--------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 26     | C_FAKE                     | Number of fake measurements (cycles with results being ignored)  O = No dummy cycles  1 = 1 dummy cycle   15 = 15 dummy cycles                                                                                                                                                        |  |  |  |  |  |  |  |

| 13, 14 | C_AVRG                     | Sample size for averaging within one conversion.  O = 1 = no averaging  8191 = maximum sample size  1st configuration bank, set by DSP_SEL_CFG_BANK = 0                                                                                                                               |  |  |  |  |  |  |  |

| 15, 16 | C_AVRG_ALT                 | Second sample size for averaging within one conversion.  O = 1 = no averaging  8191 = maximum sample size  2 <sup>nd</sup> configuration bank, set by DSP_SEL_CFG_BANK = 1. The DSP may switch between C_AVRG and C_AVRG_ALT values to have two operating modes selected by software. |  |  |  |  |  |  |  |

The Start of the next conversion depends on the selection of the measurement trigger. In continuous mode the next conversion follows immediately the previous one. In stretched mode the time interval between two conversions is defined by the conversion timer. Finally, in single conversion mode or pin trigger mode the single conversions are started individually, by serial opcode, by DSP command or by a trigger at a pin. New in PCapØ2 is the possibility that the DSP can select between to configuration settings for averaging, trigger select and conversion timer. This way it can switch between e.g. a scan mode and a measurement mode.

Table 3-5 Configure conversion, for details see registers 17 - 24

| Reg. | Configuration Parameter | Description                                                                                                                                                                                                                                                                                         |

|------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24   | C_TRIG_SEL              | First trigger selection for CDC trigger  O = Off when CONV_TIMEx = O  O = Stretched when CONV_TIMEx > O  1 = Continuous mode when CONV_TIMEx > O  1 = Single conversion when CONV_TIMEx = O  2 = Conversion timer triggered  3 = Pin triggered  1st configuration bank, set by DSP_SEL_CFG_BANK = O |

| 24           | C_TRIG_SEL_ALT | Second trigger selection for CDC trigger  O = Off when CONV_TIMEx = O  O = Streched when CONV_TIMEx > O  1 = Continuous mode when CONV_TIMEx > O  1 = Single conversion when CONV_TIMEx = O2 =  Conversion timer triggered  3 = Pin triggered  2 <sup>nd</sup> configuration bank, set by DSP_SEL_CFG_BANK = 1.  The DSP may switch between C_TRIG_SEL and  C_TRIG_SEL_ALT values to have two operating modes selected by software. |

|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24           | C_STARTONPIN   | Selects the GPIO that triggers the CDC measurement                                                                                                                                                                                                                                                                                                                                                                                  |

| 17,18,<br>19 | CONV_TIME      | Sets the conversion time in multiples of twice the period of the low-frequency clock.  tconv = 2*CONV_TIMEO*tofl  1st configuration bank, set by DSP_SEL_CFG_BANK = 0                                                                                                                                                                                                                                                               |

| 20,21,<br>23 | CONV_TIME_ALT  | Second setting for conversion time. $t_{conv} = 2*CONV\_TIMEO*t_{ofl}$ $2^{nd} \ configuration \ bank, \ set \ by \ DSP\_SEL\_CFG\_BANK = 1.$ The DSP may switch between CONV_TIME and CONV_TIME_ALT values to have two operating modes selected by software.                                                                                                                                                                       |

## 3.4 RDC Resistance-to-Digital Converter

### 3.4.1 Measuring Principle

In PCapØ2 resistance measurement is done by measuring discharge times. The measurements are ratiometric. This means the temperature-sensitive resistances are compared to fixed references. The ratio of discharge times is directly proportional to the ratio of capacitors. The discharge time is defined by the resistors and the load capacitance.

$$\frac{\tau_N}{\tau_{ref}} = \frac{R_{\theta}}{R_{ref}} \qquad \tau = k * R * C$$

### 3.4.2 Connecting Sensors

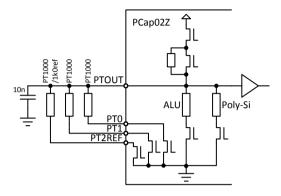

The chip device has two on-chip resistor elements for the measurement of temperature, an aluminum strip with TK  $\approx$  2800 ppm/K as a sensor and a poly-silicon resistor with TK "close to zero" as a reference. In the range 0°C to 100°C the aluminum sensor can be well approximated by a linear function of temperature.

As an alternative, it is possible to connect up to three external sensors. One of those can be used as external reference alternately. External and internal thermometers/reference may be mixed, e.g. an external PT1000 may be compared to the internal Poly-Si resistor.

In any case, it is mandatory to connect an external 10 nF capacitor, because the temperature measurement, too, is discharge time based. 10  $\mu$ s discharge time are sufficient. For the capacitor, COG ceramics yields best performance, while X7R material yields fair results.

Figure 3-14 Connecting temperature sensors

Note: The RDC measurement is based on a AC principle. So long cables with their parasitic capacitance and resistance will disturb and it is recommended to have short cables ( $\leq 0.5$ m), ideally twisted and shielded.

### 3.4.3 Cycle & Conversion

In PCapØ2 the resistance measurement is now running in three phases, like in capacitance measurement: Precharge – Full charge – Discharge. The timing is based on the internal low-frequency oscillator (OLF). The duration of the three phases can be 1 or 2 periods of this reference. The conversion starts with 2 or 8 fake measurements to improve the stability of data. For each single conversion the averaging can be selected with sample size 1, 4, 8 or 16.

Figure 3-15 RDC conversion (R\_AVRG = 1, Reference and sensor, 2 fake measurements)

# 3.4.4 Trigger

There are various possibilities to trigger a resistance measurement:

- Serial Interface command, PIN or DSP

- CDC end of conversion

- Low-frequency oscillator (OLF)

For CDC and OLF options the RDC measure rate can be reduced by setting a divider (R TRI PREDIV).

In case of the CDC option there are three ways of how the DSP is triggered:

- Parallel: The CDC end of conversion triggers RDC and CDC in parallel

- Sequentially, synchronous: The DSP is triggered by the RDC end of conversion.

Assuming that RDC rate is less than the CDC rate, the inactive RDC conversions are replaced by a delay.

- Sequentially, asynchronous: The DSP is triggered by the RDC end of conversion. If RDC rate is less than CDC rate the DSP is triggered directly from the CDC for inactive RDC conversions.

Figure 3-16 RDC Timing parallel mode

(R\_TRIG\_PREDIV = 3,R\_TRIG\_SEL = 3'b101, DSP\_START\_EN: CDC\_TRIG\_EN = 0, RDC\_TRIG\_EN = 1)

Figure 3-17 RDC Timing sequential, synchronous mode

(R\_TRIG\_PREDIV = 3, R\_TRIG\_SEL = 3'b110, DSP\_START\_EN: CDC\_TRIG\_EN = 1, RDC\_TRIG\_EN = 0)

Figure 3-18 RDC Timing sequential, asynchronous mode

(R\_TRIG\_PREDIV = 3, R\_TRIG\_SEL = 3'b101, DSP\_START\_EN: CDC\_TRIG\_EN = 0, RDC\_TRIG\_EN = 1)

### 3.5 RDC Important Parameters

## 3.5.1 Cycle Clock

The base frequency for the temperature measurement is the low frequency oscillator. By setting divider R\_OLF\_DIV the user can ensure that the period is 100µs or 80µs. A further bit, R\_CY, specifies whether 1 or 2 periods define the length of precharge phase and discharge phase.

Table 3-6 Configure cycle clock, see also register 35

| OLF Frequency | R_OLF_DIV | tprecharge = tfullcharge = tdischarge |            |  |  |  |  |  |

|---------------|-----------|---------------------------------------|------------|--|--|--|--|--|

|               |           | $R_CY = 0$                            | $R_CY = 1$ |  |  |  |  |  |

| 10 kHz        | 1         | 100 μs                                | 200 μs     |  |  |  |  |  |

| 50 kHz        | 4         | 80 µs                                 | 160 μs     |  |  |  |  |  |

| 100 kHz       | 8         | 80 µs                                 | 160 μs     |  |  |  |  |  |

| 200 kHz       | 16        | 80 µs                                 | 160 µs     |  |  |  |  |  |

Both parameters are set in register 35.

### 3.5.2 Sequence

The major settings for the sequence are the number of ports, the fakes, the reference averaging.

Table 3-7 Configure sequence, for details see registers 33, 34

| Reg. | Configuration Parameter | Description                                           |  |  |  |  |  |  |

|------|-------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| 34   | R_PORT_EN               | Enable ports PTO, PT1, PT2REF                         |  |  |  |  |  |  |

| 34   | R_PORT_EN_IREF          | Enable the internal reference resistor                |  |  |  |  |  |  |

| 34   | R_PORT_EN_IMES          | Enable the internal temperature sensor                |  |  |  |  |  |  |

| 34   | R_REF_SEL               | O = PT2REF is used for reference time (external)      |  |  |  |  |  |  |

|      |                         | 1 = IREF is used for reference (internal)             |  |  |  |  |  |  |

| 34   | R_3EXT_SEL              | O = less than 3 external sensors + external reference |  |  |  |  |  |  |

|      |                         | 1 = 3 external sensors                                |  |  |  |  |  |  |

| 32   | R_AVRG                  | Set averaging for T measurement                       |  |  |  |  |  |  |

| 33   | R_FAKE                  | Set number of fake measurements                       |  |  |  |  |  |  |

# 3.5.3 Conversion

Table 3-8 Configure conversion, for details see registers 29, 30

| Reg.         | Configuration Parameter | Description                                                                                                                |

|--------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| 29           | R_TRIG_SEL              | Selection of trigger source for RDC unit (1 <sup>st</sup> configuration bank, set by DSP_SEL_CFG_BANK = 0)                 |

| 29           | R_TRIG_SEL_ALT          | Alternative selection of trigger source for RDC unit (2 <sup>nd</sup> configuration bank set by DSP_SEL_CFG_BANK = 1)      |

| 30,31,<br>32 | R_TRIG_PREDIV           | Predivider to set the RDC rate as fraction of the CDC rate but also to the OLF_CLK when OLF_CLK is selected as RDC Trigger |

|              |                         | O = 1 = RDC conversion with each CDC conversion                                                                            |

|              |                         | 2 = RDC conversion every second CDC conversion                                                                             |

|              |                         |                                                                                                                            |

|              |                         | 2^21                                                                                                                       |

| 29           | R_STARTONPIN            | Start RDC conversion on pin trigger. Not recommended                                                                       |

# 4 Interfaces (Serial & PDM/PWM)

#### 4.1 Serial Interfaces

Two types of serial interfaces are available for communication with a microcontroller and for programming the device: SPI and IIC. Only one interface is available at a time, selected by pin IIC\_EN. On both interfaces the PCapØ2 can operate as slave only.

| IIC_EN = GROUND | 4-wire SPI interface<br>General-purpose I/O pins PGO and PG1 are not available  |

|-----------------|---------------------------------------------------------------------------------|

| IIC_EN = VDD    | 2-wire I <sup>2</sup> C interface<br>All general-purpose I/O pins are available |

IIC EN may not be floating. If no controller interface is needed connect IIC EN to VDD.

### Note:

Besides the case of reading the result registers, it is recommended to deactivate the converter for any communication to configuration registers, EEPROM, OTP or SRAM. This is done by setting the RunBit configuration register 77 to 'O'. After the communication process the RunBit needs to be set back to '1'.

### 4.1.1 Opcodes

Table 4-1 PCapØ2 Opcodes

| Description          | Byte2 |   |   |    |          |         |     |     | Ву      | te1      | ByteO        |

|----------------------|-------|---|---|----|----------|---------|-----|-----|---------|----------|--------------|

| Write to OTP         | 1     | 0 | 1 | ad | add<120> |         |     |     |         |          | data<70>     |

| Read from OTP        | 0     | 0 | 1 | ad | d<1      | 2       | .0> |     |         |          | data<70>     |

| Write to SRAM        | 1     | 0 | 0 | 1  | ad       | d<1     | 1   | .0> |         |          | data<70>     |

| Read from SRAM       | 0     | 0 | 0 | 1  | ad       | d<1     | 1   | .0> |         |          | data<70>     |

| Block write EEPROM   | 1     | 1 | 1 | 0  | 0        | 0       | 0   | 1   | da      | ta<70>   |              |

| Erase EEPROM         | 1     | 1 | 1 | 0  | 0        | 0       | 1   | 0   | 0       | add<60>  | [dummy byte] |

| Write configuration  | 1     | 1 | 0 | 0  | 0        | 0       | 0   | 0   | 0       | add<60>  | data<70>     |

| Read result          | 0     | 1 | 0 | 0  | 0        | 0       | 0   | 0   | 0       | add<60>  | data<70>     |

| Write EEPROM         | 1     | 1 | 1 | 0  | 0        | 0 0 0 0 |     | 0   | add<60> | data<70> |              |

| Read EEPROM          | 0     | 1 | 1 | 0  | 0        | 0       | 0   | 0   | 0       | add<60>  | data<70>     |

| Block erase EEPROM   | 1     | 1 | 1 | 0  | 0        | 0       | 1   | 1   |         |          |              |

| POR (Power-on Reset) | 1     | 0 | 0 | 0  | 1        | 0       | 0   | 0   |         |          |              |

| Initialize           |       | 0 | 0 | 0  | 1        | 0       | 1   | 0   |         |          |              |

| CDC Start conversion |       | 0 | 0 | 0  | 1        | 1       | 0   | 0   |         |          |              |

| RDC Start conversion |       | 0 | 0 | 0  | 1        | 1       | 1   | 0   |         |          |              |

| Terminate write OTP  |       | 0 | 0 | 0  | 0        | 1       | 0   | 0   |         |          |              |

All commands for write or read to memory or configuration / read registers may use explicit addressing or address auto-increment.

The serial interface is tested most easily by writing an arbitrary data to the SRAM and read this back.

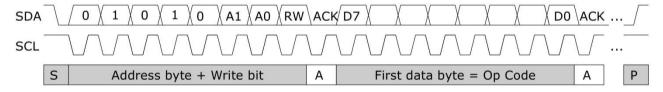

### 4.2 I<sup>2</sup>C Compatible Interface

The present paragraph outlines the PCapØ2 device specific use of the I<sup>2</sup>C interface. The external I<sup>2</sup>C master begins the communication by creating a start condition, a falling edge on the SDA line while SCL is HIGH. It stops the communication by a stop condition, a rising edge on the SDA line while SCK is high. Data bits are transferred with the rising edge of SCK.

On I<sup>2</sup>C buses, every slave holds an individual 7-bit device address. This address has always to be sent as the first byte after the start condition, the eighth bit indicating the direction of the following data transfer (R=read=1 and W=write=0).

Address byte:

| MSB   |   |   |   |   |        |    | LSB |

|-------|---|---|---|---|--------|----|-----|

| 0     | 1 | 0 | 1 | 0 | Α1     | AO | R/W |

| fixed |   |   |   |   | variab | le | key |

Default address: 40 (A1 = A0 = 0)

The address byte is followed by the opcode and eventually the payload. Each byte is followed by an acknowledge bit (= 0, when a slave acknowledges).

Figure 4-1 I<sup>2</sup>C principle sequence

#### 4.2.1 I2C Write

During write transactions, the master alone sends data, the addressed slave just sends the acknowledge bits. The master first sends the slave address plus the write bit. Then it sends the PCapØ2 specific opcode including the register address in the slave. Finally it sends the payload ("Data").

Figure 4-2 I<sup>2</sup>C Write procedure; an example ("write 'hFF as a datum to the SRAM at address 'h147.)

|   |                   | "Write RAM" |                        |   |               |   |       |   |   |  |  |

|---|-------------------|-------------|------------------------|---|---------------|---|-------|---|---|--|--|

|   |                   |             |                        |   |               |   |       |   |   |  |  |

| S | I2C-Address + W   | Α           | Opcode + Write address | Α | Write address | Α | Data  | Α | Р |  |  |

| = |                   |             |                        |   |               |   |       |   | = |  |  |

| S | 0101000 0         | 0           | 'h 91                  | 0 | 'h 47         | 0 | 'h FF | 0 | Р |  |  |

|   |                   |             |                        |   |               |   |       |   |   |  |  |

|   | write address 147 |             |                        |   |               |   |       |   |   |  |  |

#### 4.2.2 I<sup>2</sup>C Read

During read transactions, the direction of communication has to be commuted. Therefore, the master creates again a start condition and sends the slave address plus the read bit to switch into read mode. Figure 4-6 shows an example with op code "read from SRAM".

Figure 4-3  $I^2C$  Read example. "Read from SRAM address 'h147", we find 'hFF having been programmed before

|   |                 |   |                       |   |              |   |   |                 |   |       |   | • |

|---|-----------------|---|-----------------------|---|--------------|---|---|-----------------|---|-------|---|---|

| S | I2C-Address + W | Α | Opcode + Read address | Α | Read address | Α | S | I2C-Address + R | Α | Data  | N | Р |

|   |                 |   |                       |   |              |   |   |                 |   |       |   |   |

| S | 0101000 0       | 0 | 'h 11                 | 0 | 'h 47        | 0 | S | 0101000 1       | 0 | 'h FF | 1 | Р |

After arrival of the first (or any) data byte, the master may either signal

- Not-Acknowledge = N = 1 to indicate "end read", "stop sending" to the slave, or

- Acknowledge = A = O to indicate "continue in automatic address-increment mode" and thus receive many bytes in a row. As one can see, automatic address increment is particularly useful and efficient with the I<sup>2</sup>C interface.

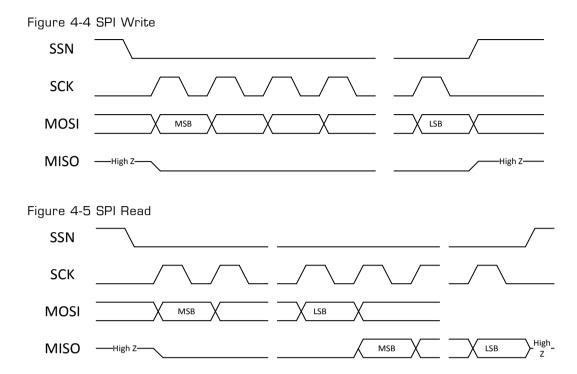

## 4.3 SPI interface

Clock Polarity, Clock Phase and Bit Order: The following choices are necessary for successful operation.

Table 4-2 SPI Clock Polarity, Clock Phase and Bit Order

| SPI - Parameter | Description        | Setting      |  |  |  |

|-----------------|--------------------|--------------|--|--|--|

| CPOL            | Clock polarity     | 0            |  |  |  |

| СРНА            | Clock phase        | 1            |  |  |  |

| Mode            | SPI Mode           | 1            |  |  |  |

| DORD            | Bit sequence order | O, MSB first |  |  |  |

Table 4-3 SPI timing parameters

| Name                                 | Symbol   | VDD=2.2 V | VDD=3.0 V | VDD=3.6 V | Units |

|--------------------------------------|----------|-----------|-----------|-----------|-------|

| Serial clock frequency               | fSPI-bus | 10        | 17        | 20        | MHz   |

| Serial clock pulse width HI state    | tpwh     | 50        | 30        | 25        | ns    |

| Serial clock pulse width LO state    | tpwl     | 50        | 30        | 25        | ns    |

| SSN enable-to-valid latch            | tsussn   | 10        | 8         | 7         | ns    |

| SSN pulse width between write cycles | tpwssn   | 50        | 30        | 25        | ns    |

| Data setup time prior to clock edge  | tsud     | 7         | 6         | 5         | ns    |

| Data hold time after clock edge      | thd      | 5         | 4         | 3         | ns    |

| Data valid after clock edge          | tvd      | 40        | 26        | 16        | ns    |

## 4.4 Special Timings

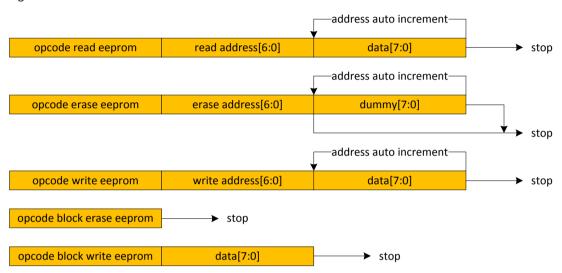

## 4.4.1 **EEPROM** Timings

Here we describe the necessary timing for communication with the EEPROM via serial interface. Only 1's can be written to the EEPROM. Therefore, it is necessary to erase the EEPROM cells before writing new data. EEPROM communication may use address auto-increment. In case of "Erase EEPROM" the incremental write is achieved by sending additional dummy bytes (e.g. 'hE2\_03\_00 will erase EEPROM cells 3 and 4).

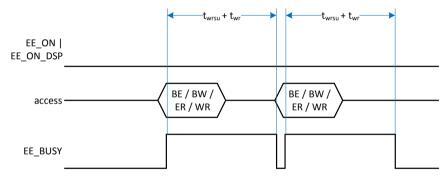

Figure 4-6 EEPROM communication

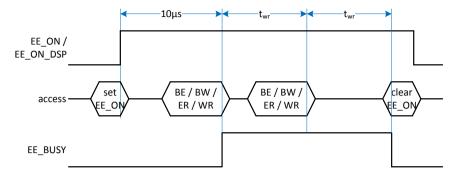

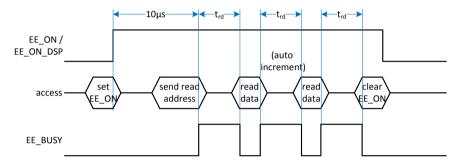

It is necessary to wake up the EEPROM before each write access. Therefore, BG\_TRIM1[3:0] needs to be set to 'h7! The EEPROM wakeup can be done explicitly or automatically (EE\_ON or EE\_ON\_DSP). It is mandatory to take care of the setup timings, for each individual byte:

|       | EE_WAKEUP_MODE |          |        |

|-------|----------------|----------|--------|

| trdsu | 0              | 1.5*tocf | 300 µs |

|       | 1              |          | 10 µs  |

| trd   | X              |          | 600 ns |

| twrsu | 0              | 1 * tocf | 200 μs |

|       | 1              |          | 10μs   |

| twr   | 0              | 34*tocf  | 6.8 ms |

Figure 4-7 EEPROM power controlled by user: Write/ Erase/ Block write/ Block erase

Figure 4-8 EEPROM power controlled by user: Read

Figure 4-9 EEPROM power controlled automatically: Write/ Erase/ Block write/ Block erase

Figure 4-10 EEPROM power controlled automatically: Read

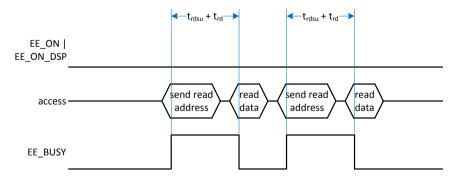

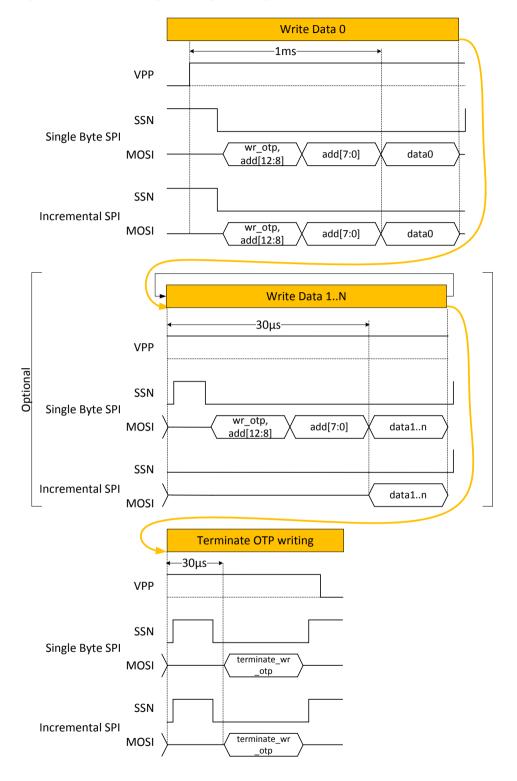

## 4.5 OTP Timings

In the un-programmed state the OTP cells' content is 'hFF. Once programmed to 'O', the bits can't be set back to '1'. Writing to the OTP demands an external programming voltage of 6.5 volts at pin VPP\_OTP. After setting the programming voltage it is mandatory to wait for 1 ms. After each data byte sent it is mandatory to wait for min. 30  $\mu$ s (max. 1000 $\mu$ s) before sending the next data or to terminate the OTP write.

#### Note:

Before reading the OTP make sure that in configuration register 1 the correct ECC\_MODE is configured.

Figure 4-11 OTP timing for programming by SPI

Figure 4-12 OTP timing for programming by I<sup>2</sup>C

## 4.6 GPIO and PDM/PWM

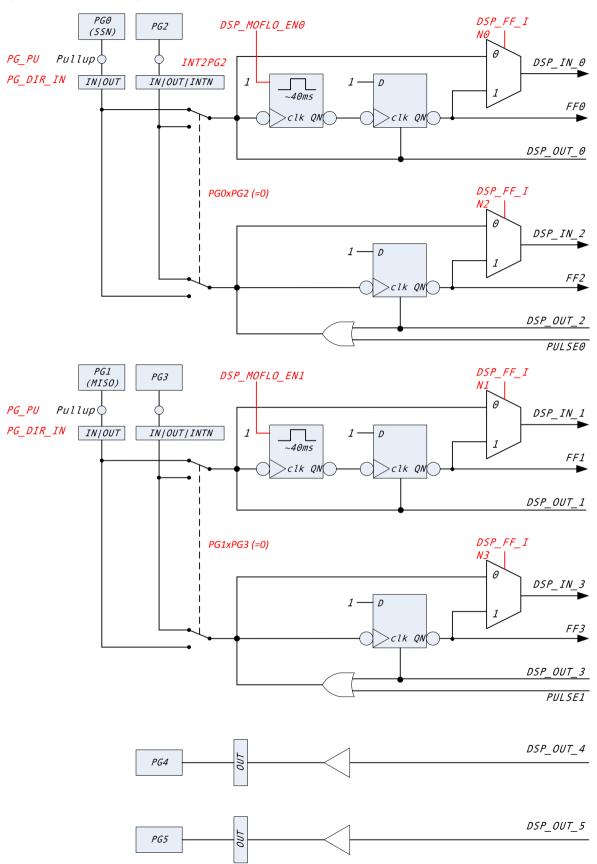

This section is about the general purpose ports and their use as Pulse-Density / Pulse Width Modulated outputs (PDM/PWM). Like PCapØ1, PCapØ2 is very flexible with assignment of the various GPIO pins to the DSP inputs/outputs. The following table shows the 5 general purpose ports and their possible assignment.

Table 4-4 General-Purpose Port Assignment

| External Port Name | Description                                   | Direction in or out |  |

|--------------------|-----------------------------------------------|---------------------|--|

| PGO                | SSN (in SPI-Mode), serial select              | in                  |  |

|                    | DSP_x_0 or DSP_x_2,<br>I/O for the DSP        | in(1) / out         |  |

|                    | FFO or FF2,<br>I/O for the DSP with Flip-Flop | in(1)               |  |

|                    | PulseO, PDM or PWM output                     | out                 |  |

| PG1                | MISO (in SPI-Mode)                            | out                 |  |

|                    | DSP_x_1 or DSP_x_3, I/O for the DSP           | in(1) / out         |  |

|                    | FF1 or FF3, I/O for the DSP with Flip-Flop    | in(1)               |  |

|                    | Pulse1, PDM or PWM output                     | out                 |  |

| PG2                | DSP_x_0 or DSP_x_2, I/O for the DSP           | in(1) / out         |  |

|                    | FFO or FF2, I/O for the DSP with Flip-Flop    | in(1)               |  |

|                    | PulseO, PDM or PWM output                     | out                 |  |

|                    | INTN                                          | out                 |  |

| PG3                | DSP_x_1 or DSP_x_3, I/O for the DSP           | in(1) / out         |  |

|                    | FF1 or FF3, I/O for the DSP with Flip-Flop    | in(1)               |  |

|                    | Pulse1, PDM or PWM output                     | out                 |  |

| PG4                | DSP_OUT_4 (output only)                       | out                 |  |

| PG5                | DSP_OUT_5 (output only)                       | out                 |  |

<sup>(1)</sup> These ports provide an optional debouncing filter and an optional pull-up resistor.

Figure 4-13 GPIO assignment

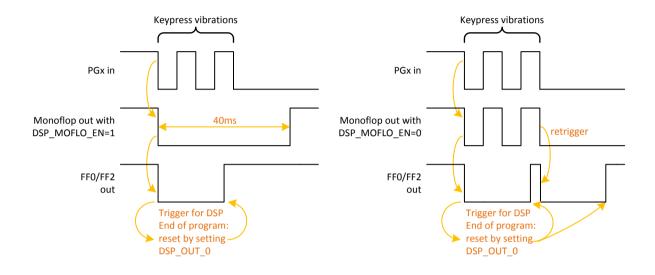

#### 4.6.1 Debouncing filter

There is a possibility to activate a 40 ms debounce filter ("monoflop") for the ports in case these are used as push button inputs. This might be useful especially in case the DSP is started by the pins (signals FFO, FF2). Figure 2-3 shows the effect of the monoflop filter.

Figure 4-14 Port trigger timing

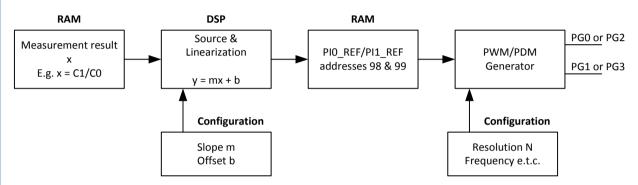

#### 4.6.2 PDM/PWM

There is a possibility to generate two pulse width modulated or pulse density modulated output signals. In general, PDM is preferred because of better noise behavior. The output is based on the content of RAM registers PIO\_REF, PI1\_REF (DSP write addresses 98, 99. Width 16 bit each). The content of those RAM cells depends on the firmware. The description in this datasheet is based on the standard firmware, which writes the capacitance ration to PIO\_REF, the Resistance ratio to PI1 REF.

The pulse interfaces can be switched on individually. The resolution can be programmed from 10 to 16 bit. There is a broad range of clock signals that can be selected as base for the pulse interfaces, derived from the 50 kHz low-frequency oscillator, the 4 MHz high-frequency oscillator or an internal ring oscillator with up to 20MHz or the cycle time. The output pins may be PGO or PG2 and PG1 or PG3.

Figure 4-15

Filter configuration instructions:

The resistor should be >= 50 kOhm

The internal DC resistance of the output buffer is typ. 100 Ohm

1.Settling time (for PDM and PWM)

If the output value changes, the settling time to reach 90% is 2.3 x Tau

Tau=R x C

Example:  $200k \times 100nF \times 2.3 = 50 ms$

The smaller is Tau the faster is the settling but the higher is the ripple.

2. Voltage Ripple

Calculation method: T.b.d.

The output signal can be converted into an analog voltage through a low-pass filter. For the PDM output a first-order filter made of 220 k $\Omega$  / 100 nF is sufficient. The PWM output needs a filter with a lower cutoff frequency.

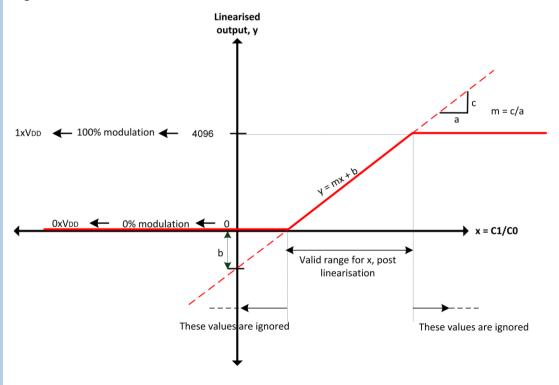

In the standard firmware, the result of measurement from capacitance or temperature is a 24-bit value. The DSP linearizes this 24 bit result to a 12 bit value (assuming '12 bit resolution' setting). The parameters Slope (m) and Offset (b) of the linear function are configurable in parameter registers 59 – 70. Both, offset and slope can be set to either positive or negative values. The setting of the slope and offset limits the range of the output signal and hence determines the voltage range of the filtered analog signal. A 12-bit resolution thus limits the result value between 0 and 4096. For lower-bit resolutions, the range reduces accordingly. The following figure depicts how the result is processed to generate the pulsed output.

Figure 4-16 PWM-PDM pulse generation

The following figure shows a sample linear function and its parameters graphically. In this graph, the result C1/C0 has been taken on the x-axis, assuming that this result is to be pulse modulated. Here the value of m is positive and b is negative. A 12 bit resolution has been configured.

Figure 4-17 PWM-PDM linearization

By setting the value of m and b, the linearization function limits the range of the output x as shown. Values outside these limits are ignored. Thereby knowing the range in which the results might change, the parameters of the linearization function can be fed accordingly. The lower limit of the valid range corresponds to 0% modulation (all bits are 0), The upper limit of the valid range corresponds to 100% modulation (all bits are 1), and this is the maximum possible value of output. 12 bit resolution implies that this maximum value is 4096. For lower-bit resolutions, this maximum value will come down accordingly. In terms of voltage, the two limits correspond to OV and VDD.

#### Applications:

- A typical case would be outputting capacitance results through PGO and temperature results through PG1. Calculation and transfer to the output registers will be performed by firmware.

- Main application will be when an analog interface is demanded by the final customer.

- Other applications concern maybe an impossibility to use the serial interface (speed limitations or other concerns).

- Finally, a temperature-coded pulse stream could be low-pass filtered and then directly used for temperature control.

Please note that the entire linearization task as described here is performed by firmware, especially the standard firmware.

#### 4.7 Interfaces Parameters

#### 4.7.1 GPIO Settings

Table 4-5

| Reg | Configuration | Description                                                                                                                                                                    |

|-----|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | Parameter     |                                                                                                                                                                                |